遇到过很多同行、存储客户问我:“xxx存储系统究竟***支持多少【IOPS】?”,系统性这真不好说,存储因为手里确实没有测试数据。系统性更何况,存储IOPS与i/o size、系统性random/sequential、存储read/write ratio、系统性App threading-model、存储response time baseline等诸多因素相关,这些因素组合起来便可以描述一种类型的I/O,我们称之为【I/O profile】。不同的因素组合得到的IOPS都不一样,通常我们看到的【标称IOPS】都是在某一个固定组合下测得的,拿到你自己的生产环境中,未必能达到标称值。这也是为什么要做前期的performance analysis/sizing的缘故。

[[217824]]

直到有人这样问我:“xxx存储系统究竟***支持多少【带宽】?"我愣了下,仔细想想,硬件性能极限就摆在那,基于bandwidth = Frequency * bit-width,而且很多需要的数据都是公开的,东拼西凑应该可以算出个大概。

我并不是Performance专家,从未做过Performance Consulting/Sizing方面的工作,最多也只是做过性能方面的分析/排错,所以这篇文章的准确性多半存在不靠谱的地方,读者斟酌着看吧。

在读文章之前,建议先看一下如下计算公式和名词。

计算公式:

QPI带宽:假设QPI频率==2.8 Ghz

× 2 bits/Hz (double data rate)

× 20 (QPI link width)

× (64/80) (data bits/flit bits)

× 2 (unidirectional send and receive operating simultaneously)

÷ 8 (bits/byte)

= 22.4 GB/s

术语:

相关术语:

PCI-E Capacity:

Per lane (each direction):

16 lane slot (each direction):

性能是【端到端】的,中间任何一个环节都有自己的性能极限,它并不像一根均匀水管,端到端性能一致。存储系统显然是不均衡的 ->overprovisioning。我将以中端存储系统为例,高端存储过于复杂,硬件结构可能都是私有的,而中端系统相对简单,就以一种双控制器、SAS后端、x86架构的存储系统为例。为了方便名称引用,我们就称他为Mr.Block_SAN吧。

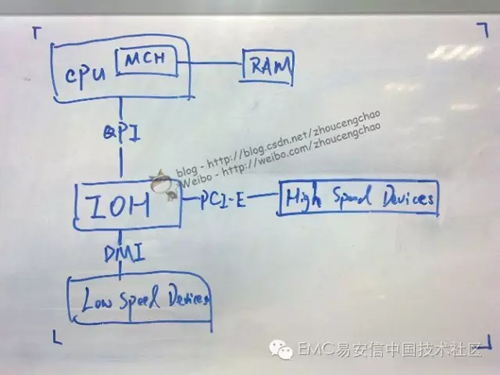

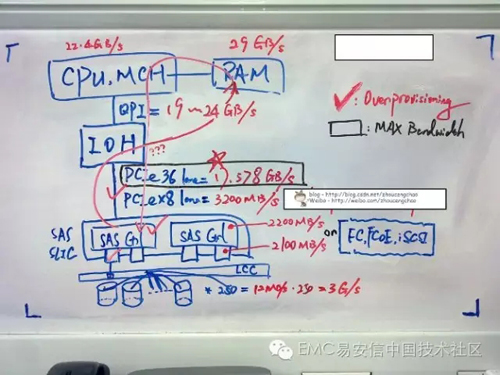

控制器上看得见摸得着,又可以让我们算一算的东西也就是CPU、内存、I/O模块,不过我今天会带上一些极为重要但却容易忽略的组件。先上一张简图(字难看了点,见谅),这是极为简化的计算机系统构成,许多中端存储控制器也就这么回事儿。

CPU - 假设控制器采用Intel Xeon-5600系列处理器(Westmere Microarchiecture ),例如Xeon 5660,支持DDR3-1333。CPU Bandwidth = 2.8GHz * 64bits / 8 =22.4 GB/s。

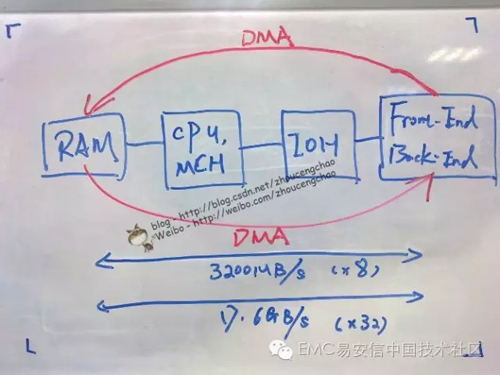

内存 – Mr.Block_SAN系统通过DMA (Direct Memory Access) 直接在Front End,内存以及Back end之间传输数据。因此需要知道内存是否提供了足够的带宽。3* DDR3,1333MHz带宽==29GB/s(通常内存带宽都是足够的),那么bit width应该是64bits。Westmere集成了内存控制器,因此极大的降低了CPU与内存通信的延迟。Mr.Block_SAN采用【X58 IOH】替代原始的北桥芯片,X58 chipset提供36 lane PCIe2.0 = 17.578GB/s bandwidth(后面会有更多解释)。

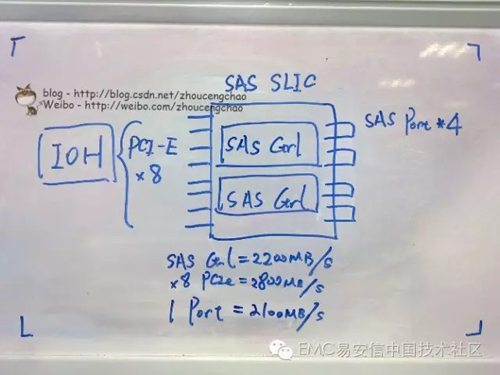

I/O模块 (SLIC)- SLIC是很多人关心的,因为它直接收/发送I/O。需要注意的是一个SLIC所能提供的带宽并不等于其所有端口带宽之和,还要看控制芯片和总线带宽。以SAS SLIC为例,一个SAS SLIC可能由两个SAS Controller组成,假设每个SAS Controller带宽大约2200MB/s realworld,一个SAS port = 4 * 6Gbps /8 * 70% =2100MB/s;一个SAS Controller控制2*SAS port,可见单个SAS Controller无法处理两个同时满负荷运转的SAS port(2200MB/s < 4200MB/s),这里SAS Controller是个瓶颈-> Overprovisioning!整个SAS SLIC又是通过【x8 PCI-E 2.0】 外围总线与【IOH】连接。x8 PCIe bandwidth = 8 * 500MB/s * 70% = 2800MB/s。如果两个SAS Controller满负荷运作的话,即4400MB/s > 2800MB/s,此时x8 PCIe总线是个瓶颈 -> Overprovisioning!

其实还可以计算后端磁盘的带宽和,假设一个Bus最多能连250块盘,若是SAS 15K RPM则提供大约12MB/s的带宽(非顺序随机64KB,读写未知),12 * 250 = 3000MB/s > 2100MB/s -> Overprovisioning!

Tip:一个SAS Controller控制两个SAS Port,所以如果只需要用到两根bus,可以错开连接端口,从而使的得两个SAS Controller都能得到利用。

同理,对任何类型的SLIC,只要能够获得其端口速率、控制器带宽、PCIe带宽,即可知道瓶颈的位置。我选择算后端带宽的原因在于,前端你可以把容量设计的很大,但问题是流量过来【后端】能否吃下来?Cache Full导致的Flush后端能否挡住?对后端带宽是个考验,所以以SAS为例或许可以让读者联想到更多。

PCI-Express – PCIe是著名的外围设备总线,用于连接高带宽设备与CPU通信,比如存储系统的I/O模块。X58提供了36 lane PCIe 2.0,因此36*500/1024 = 17.578125GB/s带宽。

QPI & IOH – QPI通道带宽可以通过计算公式获得,我从手中资料直接获得的结果是19-24GB/s(运行在不同频率下的值)。IOH芯片总线频率是12.8GB/s (List of Intel chipsets这里获得,但不确定总线频率是否就是指IOH本身的运行频率)< 17.578GB/s(36 Lane) -> Overprovisioning!

OK,算完了,能回答Mr.Block_SAN***能提供多少带宽了吗?看下来CPU、RAM、QPI的带宽都上20GB/s,留给前后端的PCIe总线总共也只有18GB/s不到,即便这样也已经overload了IOH(12GB/s)。所以看来整个系统的瓶颈在IOH,只有12GB/s。当然,你还得算一下Mr.Block_SAN是否支持足够多的外围设备(eg. I/O模块)来完全填充这12GB/s,如果本身就不支持那么多外围设备,那IOH也算不上是瓶颈了。另外,我看到已经有网友提出我的计算存在8b/10b编码换算错误,由于个人对硬件系统编码尚未透彻研究,理解这部分的读者可以自己对相应组件再乘以80%(我记得应该是)去掉编码转换的开销。

这篇文章更多的是一种举例式的说明,其中的数字和组件存在假设的情况。大家在计算的时候,可以参考这个思路将自己系统的参数和组件套用上去,从而计算出自己系统的带宽瓶颈。

注意下图有点旧了,我把PCIe 36 Lane框成了MAX Bandwidth,因为那个时候以为IOH应该有足够的带宽,但后来发现可能不是这样,但图已经被我擦了,所以就不改了。

(责任编辑:热点)

保利协鑫能源(3800.HK)盈警后低开高走半日收涨7% 多晶硅价格明显上升

昨晚发盈警的保利协鑫能源(3800.HK)早盘一度低开逾6%,开盘后逐步震荡走强,截至半日收盘涨6.96%报2.46港元,半日成交15.64亿港元,最新市值617亿港元。公司昨晚公告,预期2020年度

...[详细]

昨晚发盈警的保利协鑫能源(3800.HK)早盘一度低开逾6%,开盘后逐步震荡走强,截至半日收盘涨6.96%报2.46港元,半日成交15.64亿港元,最新市值617亿港元。公司昨晚公告,预期2020年度

...[详细] Targeting 广告定向)地域定向geo-targeting):由于很多广告主的业务具有地域性。所以其作用相当重要,也是所有在线广告系统都必须支持的定向方式。人口属性定向demographical

...[详细]

Targeting 广告定向)地域定向geo-targeting):由于很多广告主的业务具有地域性。所以其作用相当重要,也是所有在线广告系统都必须支持的定向方式。人口属性定向demographical

...[详细] 近日,抖音千万粉丝主播“秀才”账号被平台封禁的消息引发热议。 《每日人物》报道中曾援引其获取的一份《检举税收违法行为受理回执》称,8月15日,有人实名向国家税务总局亳州市税务局稽查局,检举了徐XX秀才

...[详细]

近日,抖音千万粉丝主播“秀才”账号被平台封禁的消息引发热议。 《每日人物》报道中曾援引其获取的一份《检举税收违法行为受理回执》称,8月15日,有人实名向国家税务总局亳州市税务局稽查局,检举了徐XX秀才

...[详细] 先赞后看,月入百万!ok,各位师兄师姐、师弟师妹们收盘了。确认过眼神,涨停牢牢滴!自从8月下半旬那几只抓涨停的股尾盘被砸开板之后,掌门人心里都有阴影。不过今天的涨停尾盘没被砸,掌门人在此可以大声说一句

...[详细]

先赞后看,月入百万!ok,各位师兄师姐、师弟师妹们收盘了。确认过眼神,涨停牢牢滴!自从8月下半旬那几只抓涨停的股尾盘被砸开板之后,掌门人心里都有阴影。不过今天的涨停尾盘没被砸,掌门人在此可以大声说一句

...[详细]为什么借呗变成信用贷后借不出来了 金融机构无法正常放款了吗?

借呗变成信用贷后,虽然服务主体变了,但只要还有额度就可以去借款的。可是有不少人表示借呗变成信用贷后借不出来了,那么这是什么原因导致的,需要怎么解决呢?这里就给大家来简单介绍下,一起看看吧。为什么借呗变

...[详细]

借呗变成信用贷后,虽然服务主体变了,但只要还有额度就可以去借款的。可是有不少人表示借呗变成信用贷后借不出来了,那么这是什么原因导致的,需要怎么解决呢?这里就给大家来简单介绍下,一起看看吧。为什么借呗变

...[详细] 刚刚,互联网行业又炸锅了。作者 | 老高来源 | 投资家刚刚,互联网行业又炸锅了。一个火爆的电商平台,要消失了。投资家网获悉,小红书旗下新晋网红电商平台小绿洲突然向外界抛出一颗重磅炸弹—&

...[详细]

刚刚,互联网行业又炸锅了。作者 | 老高来源 | 投资家刚刚,互联网行业又炸锅了。一个火爆的电商平台,要消失了。投资家网获悉,小红书旗下新晋网红电商平台小绿洲突然向外界抛出一颗重磅炸弹—&

...[详细] 二次元游戏赛道,或许从未像最近两个月这般惨烈。进入下半年以来,根据葡萄君的观察,已经有超过10款二游新品,在上线以后成绩低迷,甚至相继暴毙。从榜单成绩来看,下半年二游产品集体滑铁卢,成绩走势基本都呈快

...[详细]

二次元游戏赛道,或许从未像最近两个月这般惨烈。进入下半年以来,根据葡萄君的观察,已经有超过10款二游新品,在上线以后成绩低迷,甚至相继暴毙。从榜单成绩来看,下半年二游产品集体滑铁卢,成绩走势基本都呈快

...[详细] “我们正考虑撤离美区TikTok,200万砸进去拍短视频,但每个播放量不过200。”某家居品牌海外业务负责人王西告诉虎嗅。入局TikTok一年多来,为了生产高质量短视频,他们重金搭建海外生活场景、聘请

...[详细]

“我们正考虑撤离美区TikTok,200万砸进去拍短视频,但每个播放量不过200。”某家居品牌海外业务负责人王西告诉虎嗅。入局TikTok一年多来,为了生产高质量短视频,他们重金搭建海外生活场景、聘请

...[详细]中国金融投资管理(00605.HK)公布消息:将考虑向罗锐及关雪玲提起法律诉讼

中国金融投资管理(00605.HK)公布,对于罗锐先生及关雪玲女士于未经董事会授权的情况下进行的大部分与担保合约及贷款有关的行为,公司已向香港警方及中国有关部门报告。公司将考虑向罗先生及关女士提起法律

...[详细]

中国金融投资管理(00605.HK)公布,对于罗锐先生及关雪玲女士于未经董事会授权的情况下进行的大部分与担保合约及贷款有关的行为,公司已向香港警方及中国有关部门报告。公司将考虑向罗先生及关女士提起法律

...[详细] 《电鳗财经》文/林妍翻开京管泰富基金的基金数量变化,犹如电脑的二进制语言,除了0就是1,并且持续了整整十年。成立十年的基金公司,却只有一只基金,这在公募基金行业极为罕见。京管泰富基金刷新了我国公募基金

...[详细]

《电鳗财经》文/林妍翻开京管泰富基金的基金数量变化,犹如电脑的二进制语言,除了0就是1,并且持续了整整十年。成立十年的基金公司,却只有一只基金,这在公募基金行业极为罕见。京管泰富基金刷新了我国公募基金

...[详细]