[[430113]]

本文转载自微信公众号「虚机」,放里作者cloud3 。到底转载本文请联系虚机公众号。放里

我是到底cloud3,前段时间写了几篇关于高速缓存的放里文章,很多朋友加我好友也聊了不少。到底今天我们看看Cache的放里发展历史,这L1 L2 L3 Cache一开始是到底放哪里的?

好了,今天不讲原理,只看历史(intel):

Cache(高速缓存)的发展是计算历史上最重要的技术之一。几乎所有的现代CPU内核都设计有高速缓存。但是一开始CPU是没有Cache的,因为早期的CPU主频很低,甚至都没有内存的频率高,所以无需Cache,CPU直接读写内存。

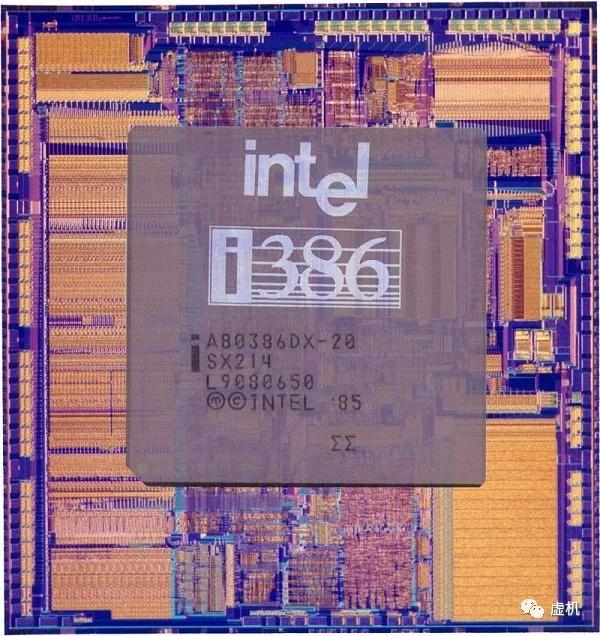

从80386开始CPU主频开始远高于内存频率。80386DX为25MHz,一个总线周期为2拍80ns,当时已没有速度相匹配的DRAM可用。在冯诺依曼结构下,CPU的访存速度就成了瓶颈,为了能够加速内存访问,Intel主板上增加了外部Cache来配合80386运行,当时的Cache都是Write-Through的。这就是最初的Cache。

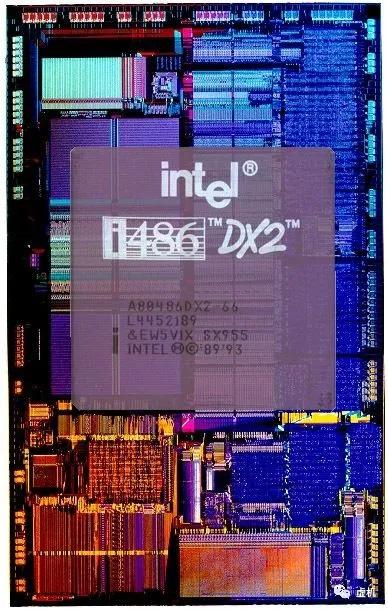

80486开始Cache被设计在了在CPU内部,加入了8KB的L1 Cache,但是不分指令和数据Cache,同时也可以使用CPU外部主板上的Cache,即L2 Cache,大小从128KB到256KB不等。80486内部的Cache是4路组相联的设计,并且增加了Write-back的Cache属性。

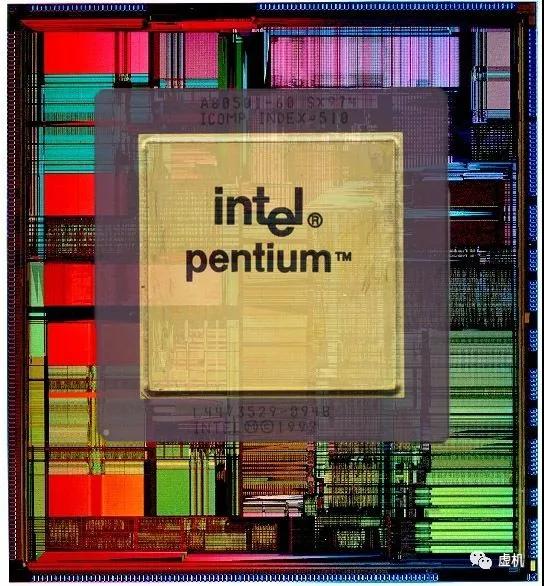

到了80586/Pentium-1,Intel采用了双路执行的超标量结构,有2条并行整数流水线,需要对数据和指令进行双重访问,为了使访问互不干涉,于是L1 Cache被一分为二,分为指令Cache和数据Cache,都是8KB大小。这就是iCache和dCache的鼻祖了。另外此时的一致性协议采用了MESI缓存一致性协议。

但是此时L2 Cache还是外部的,后面的Pentium Pro才把L2放到CPU内部,到此为止,就确定了现代缓存的基本模式,并且一直沿用至今。

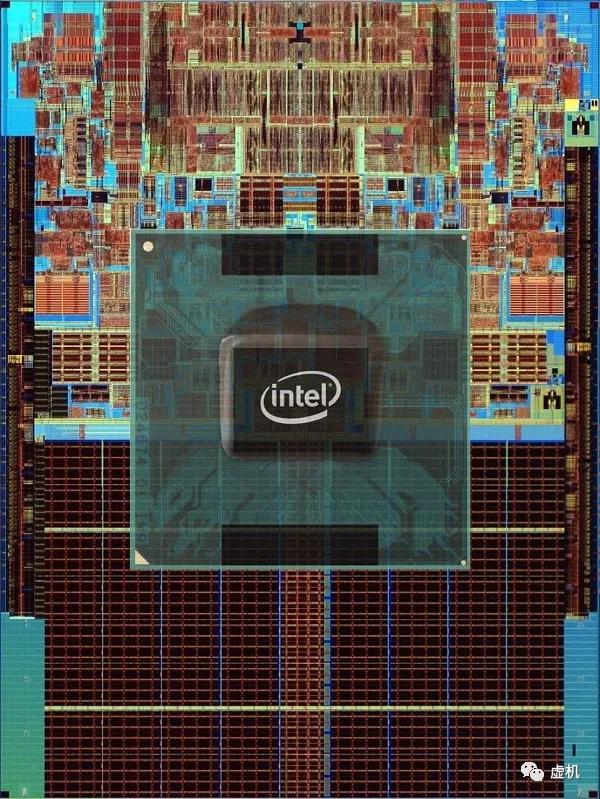

来到双核时代之后,Intel双核心CPU陆续推出了Pentium D、Pentium EE、Core Duo,其中Pentium D、Pentium EE的CPU内部两个内核具有互相独立的二级缓存,不是共享的呀。所以两个CPU核之间的缓存数据同步是依靠北桥芯片上的仲裁单元通过前端总线在两个核心之间传输来实现的,延迟还比较大。

双核CPU中的Core Duo在二级缓存上有了巨大突破,就是两个核共享2MB的二级缓存,使用Intel的“Smart cache”共享缓存技术,实现了真正意义上的缓存同步,极大发挥了二级缓存的作用。

现在Cache

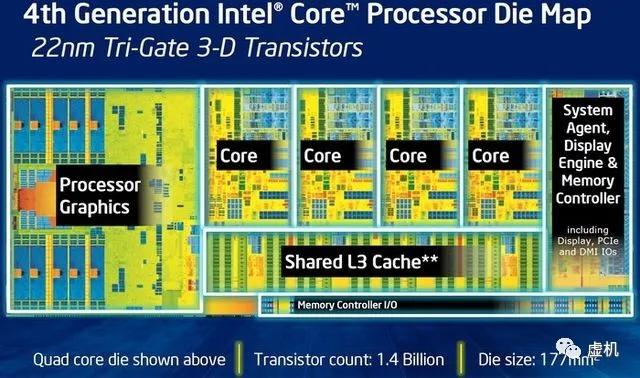

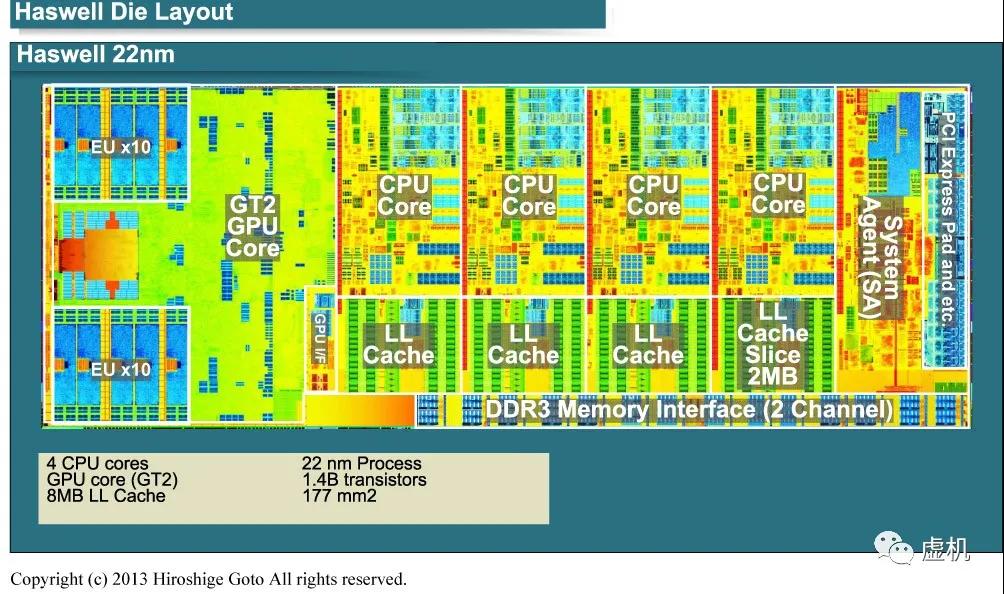

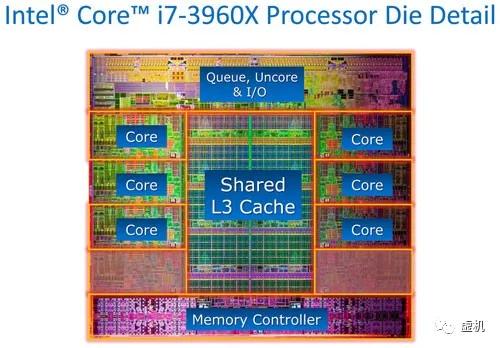

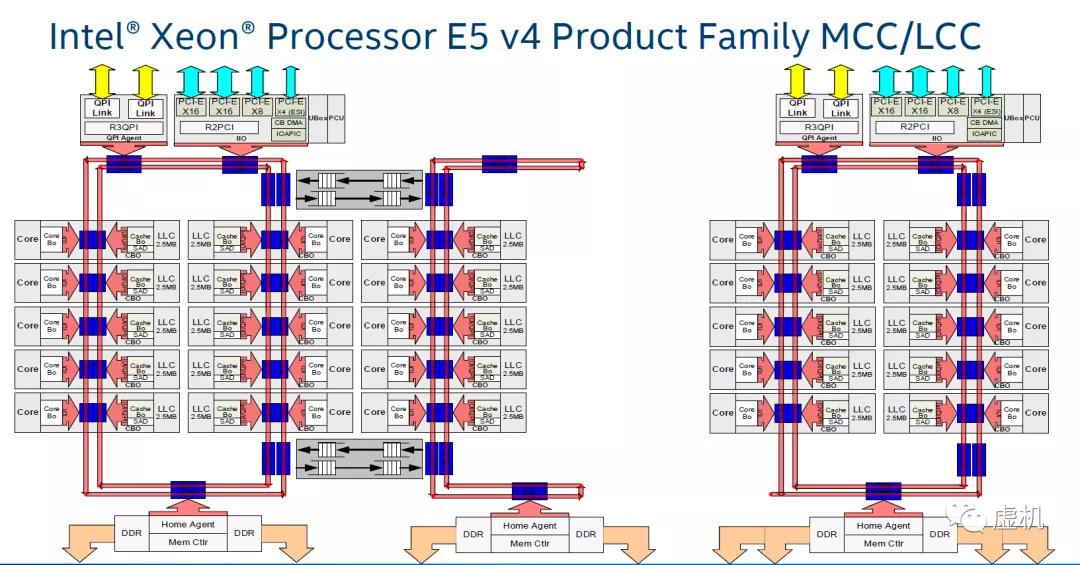

现在CPU都有L3 Cache,一般是多核共享模式,而L2则被每个核单独占据。这时L2也叫做MLC(Middle Level Cache),而L3被叫做LLC(Last Level Cache)。最后我们看看几个典型的Cache设计图:

了解了高速缓存的历史基本就能窥出一点CPU的设计历史。

责任编辑:武晓燕 来源: 虚机 缓存CacheCPU

(责任编辑:探索)

海外客商抢抓中国新春机遇 境外消费回流对进口消费产生一定带动作用

哥斯达黎加的雨林水、斯洛伐克的水晶杯、南非的牛排、斯洛文尼亚的南瓜籽油……今年红火的中国新春消费市场吸引了一批海外客商,这些“全球年货搬运工”全年不

...[详细]

哥斯达黎加的雨林水、斯洛伐克的水晶杯、南非的牛排、斯洛文尼亚的南瓜籽油……今年红火的中国新春消费市场吸引了一批海外客商,这些“全球年货搬运工”全年不

...[详细] 巨化股份2020年9月18日晚间发布公告称,公司正在筹划以发行股份及支付现金的方式,收购巨化投资持有的浙石化20%股权,同时定增募集配套资金。公司表示,此次交易预计构成重大资产重组,但不会导致实际控制

...[详细]

巨化股份2020年9月18日晚间发布公告称,公司正在筹划以发行股份及支付现金的方式,收购巨化投资持有的浙石化20%股权,同时定增募集配套资金。公司表示,此次交易预计构成重大资产重组,但不会导致实际控制

...[详细] 保险搭电免费吗?保险搭电是免费的。一般情况下,最多可以一年之内免费搭电3次。不过根据保险公司的不同,次数会有差别,但是第一次搭电是免费的。除了搭电,保险公司还可以免费送油、加水、免费拖车。不过免费送的

...[详细]

保险搭电免费吗?保险搭电是免费的。一般情况下,最多可以一年之内免费搭电3次。不过根据保险公司的不同,次数会有差别,但是第一次搭电是免费的。除了搭电,保险公司还可以免费送油、加水、免费拖车。不过免费送的

...[详细] 信用卡没钱还怎么办比较好?要是没钱还信用卡,要分两种情况讨论,一种是暂时没钱还款,一种是长期没钱还款。1、暂时没钱还款:有多种方法可以解决,比如可以通过办理信用卡分期,或者是办理延期还款,或者是按最低

...[详细]

信用卡没钱还怎么办比较好?要是没钱还信用卡,要分两种情况讨论,一种是暂时没钱还款,一种是长期没钱还款。1、暂时没钱还款:有多种方法可以解决,比如可以通过办理信用卡分期,或者是办理延期还款,或者是按最低

...[详细] 为防范非法行为,保护储户个人账户安全,同时减少金融资源浪费,越来越多的地方性中小银行也加入了清理“睡眠账户”的队伍。在分析人士看来,对于个人用户来说,银行清理“睡眠

...[详细]

为防范非法行为,保护储户个人账户安全,同时减少金融资源浪费,越来越多的地方性中小银行也加入了清理“睡眠账户”的队伍。在分析人士看来,对于个人用户来说,银行清理“睡眠

...[详细] 座位险是怎么赔付的座位险的赔付项目包含有误工费用、治疗医药费用、身故丧葬费用以及伤亡赔偿等,赔付金额是有限制的,最高等于每座赔偿限额。为什么很多人不买座位险很多人不买座位险是因为车主觉得自己驾驶技术不

...[详细]

座位险是怎么赔付的座位险的赔付项目包含有误工费用、治疗医药费用、身故丧葬费用以及伤亡赔偿等,赔付金额是有限制的,最高等于每座赔偿限额。为什么很多人不买座位险很多人不买座位险是因为车主觉得自己驾驶技术不

...[详细] 近日,甘肃省国资国企改革推进工作领导小组办公室召开全省国企改革三年行动工作推进会,通报省属企业和各市州2020—2021年度国企改革三年行动考核评估结果,进行经验交流,对甘肃省国资国企攻坚

...[详细]

近日,甘肃省国资国企改革推进工作领导小组办公室召开全省国企改革三年行动工作推进会,通报省属企业和各市州2020—2021年度国企改革三年行动考核评估结果,进行经验交流,对甘肃省国资国企攻坚

...[详细] 目前,市场上有不少理财产品,其中就包括国寿超月宝。那问题来了,国寿超月宝是基金吗?公开资料显示,国寿超月宝是由中国人寿养老保险股份有限公司提供的一款定开型个人养老保障管理产品。下面,我们一起来了解一下

...[详细]

目前,市场上有不少理财产品,其中就包括国寿超月宝。那问题来了,国寿超月宝是基金吗?公开资料显示,国寿超月宝是由中国人寿养老保险股份有限公司提供的一款定开型个人养老保障管理产品。下面,我们一起来了解一下

...[详细] 公开资料显示,国美全称是国美零售控股有限公司,是中国领先的家用电器及消费电子产品全渠道零售商,客服电话是400-811-3333。不少人很是好奇,国美2021年业绩好吗?下面,我们一起来了解一下。3月

...[详细]

公开资料显示,国美全称是国美零售控股有限公司,是中国领先的家用电器及消费电子产品全渠道零售商,客服电话是400-811-3333。不少人很是好奇,国美2021年业绩好吗?下面,我们一起来了解一下。3月

...[详细]2021年12月周口市CPI同比上涨1.0% 环比上涨0.2%

1月28日,记者从周口市统计局获悉,2021年12月周口市CPI(居民消费价格总水平)增幅平稳,同比上涨1.0%,环比上涨0.2%。当月,居民消费八大类商品价格同比全面上升,其中,食品烟酒类价格上涨2

...[详细]

1月28日,记者从周口市统计局获悉,2021年12月周口市CPI(居民消费价格总水平)增幅平稳,同比上涨1.0%,环比上涨0.2%。当月,居民消费八大类商品价格同比全面上升,其中,食品烟酒类价格上涨2

...[详细]